# PCI Master/Target MegaCore Function with DMA

### April 1997, ver. 1

#### Data Sheet

# Features

- pci\_a MegaCore<sup>™</sup> function implementing a 32-bit peripheral component interconnect (PCI) interface

- Optimized for FLEX<sup>®</sup> 10K architecture

- Hardware tested

- Dramatically shortens design cycles

- Simulation circuit board included

- Extensive simulation testing

- Includes test vectors

- OpenCore<sup>™</sup> feature allows designers to instantiate and simulate designs in MAX+PLUS<sup>®</sup> II prior to purchase

- Uses approximately 950 FLEX logic elements (LEs), which is about 50% the capacity of an EPF10K30 device

- Fully-compliant design (see "Compliance Summary" on page 3), including

- 32-bit, 33-MHz operation

- Simplified local side (DMA control engine) interface

- Fully simulated with required protocol test scenarios

- Hardware tested

- PCI master features:

- Memory read/write

- Bus parking

- Fully integrated DMA engine including address counter register, byte counter register, control & status register, interrupt status register

- Configurable interrupt source, including DMA terminal count, master abort, target abort, local side interrupt

- 64-byte (16 double words or DWORDS) RAM buffer implemented in FLEX 10K embedded array blocks (EABs)

- Zero wait state PCI read (107 Mbytes per second); zero wait state PCI write (102 Mbytes per second)

- PCI target features:

- Type zero configuration space

- Parity error detection

- Memory read/write and configuration read/write

- Target abort, retry, and disconnect

- 1 Mbyte of target space

- Configuration registers: device ID, vendor ID, status, command, class code, revision ID, header type, latency timer, one memory base address, subsystem ID, subsystem vendor ID, maximum latency, minimum grant, interrupt pin, and interrupt line

| Introduction | This data sheet provides operating information for the pci_a Me<br>function and includes the following topics: | gaCore |

|--------------|----------------------------------------------------------------------------------------------------------------|--------|

|              | Ordering Information                                                                                           |        |

|              | General Description                                                                                            |        |

|              | Compliance Summary                                                                                             |        |

|              | PCI Bus Signals                                                                                                |        |

|              | Local Side Signals                                                                                             |        |

|              | Function Prototype                                                                                             |        |

|              | Parameters                                                                                                     |        |

|              | Functional Description                                                                                         | 10     |

|              | Sustained Tri-State Signal Operation                                                                           | 11     |

|              | Master Device Signals & Signal Assertion                                                                       | 12     |

|              | Target Device Signals & Signal Assertion                                                                       |        |

|              | Parity Signal Operation                                                                                        |        |

|              | Bus Master Commands                                                                                            | 15     |

|              | Configuration Registers                                                                                        | 15     |

|              | Vendor ID Register (Offset = 00 Hex)                                                                           | 17     |

|              | Device ID Register (Offset = 02 Hex)                                                                           |        |

|              | Command Register (Offset = 04 Hex)                                                                             | 18     |

|              | Status Register: (Offset = 06 Hex)                                                                             | 19     |

|              | Revision ID Register (Offset = 08 Hex)                                                                         | 20     |

|              | Class Code Register (Offset = 09 Hex)                                                                          |        |

|              | Latency Timer Register (Offset = 0D Hex)                                                                       | 20     |

|              | Header Type Register (Offset = 0E Hex)                                                                         | 21     |

|              | Base Address Register Zero (Offset = 10 Hex)                                                                   | 21     |

|              | Subsystem Vendor ID Register (Offset = 2C Hex)                                                                 | 22     |

|              | Subsystem ID Register (Offset = 2E Hex)                                                                        | 22     |

|              | Interrupt Line Register (Offset = 3C Hex)                                                                      | 22     |

|              | Interrupt Pin Register (Offset = 3D Hex)                                                                       | 23     |

|              | Minimum Grant Register (Offset = 3E Hex)                                                                       | 23     |

|              | Maximum Latency Register (Offset = 3F Hex)                                                                     | 23     |

|              | PCI Bus Transactions                                                                                           | 24     |

|              | Target Transactions                                                                                            |        |

|              | Configuration Transactions                                                                                     | 30     |

|              | Master Transactions                                                                                            | 32     |

|              | DMA Operation                                                                                                  |        |

|              | Target Address Space                                                                                           | 39     |

|              | Internal Target Registers Memory Map                                                                           | 39     |

|              | DMA Registers                                                                                                  | 40     |

|              | DMA Transactions                                                                                               |        |

|              | General Programming Guidelines                                                                                 | 47     |

|              | Applications                                                                                                   |        |

|              | PCI SIG Protocol Checklists                                                                                    |        |

|              | PCI SIG Test Bench Summary                                                                                     | 59     |

|              | References                                                                                                     | 65     |

# Ordering Information

General Description The Altera<sup>®</sup> pci\_a ordering code is PLSM-PCI/A. The maintenance agreement ordering code is PLAESW-MCORE.

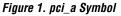

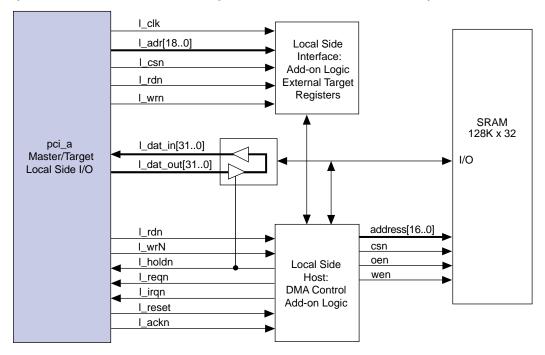

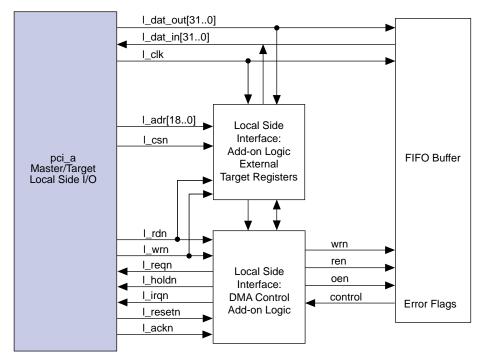

The pci\_a MegaCore function provides a timely solution for integrating 32-bit PCI peripheral devices, and is fully tested to meet the requirements of the PCI specification. The pci\_a is optimized for the EPF10K30RC240-3 device, reducing the design task and enabling designers to focus efforts on the custom logic surrounding the PCI interface. The pci\_a function is intended for use in Altera FLEX 10K devices with remaining logic resources available for user-defined local side (DMA control engine) customization. See Figure 1.

# **Compliance Summary**

The pci\_a function is compliant with the requirements specified in the PCI Special Interest Group's (SIG) *PCI Local Bus Specification, Rev. 2.1,* and *Compliance Checklist, Rev. 2.1*. The pci\_a function was verified using the applicable scenarios listed in Table 1. For a detailed listing of tests performed, see "PCI SIG Test Bench Summary" on page 59.

| Test<br>Scenario # | Test Scenario Description                                                | Simulation<br>File Name<br>Note (1) |

|--------------------|--------------------------------------------------------------------------|-------------------------------------|

| 1.1                | PCI bus device speed                                                     | pcicc101                            |

| 1.2                | PCI bus single data phase target abort cycles                            | pcicc102                            |

| 1.3                | PCI bus single data phase target retry cycles                            | pcicc103                            |

| 1.4                | PCI bus single data phase target disconnect cycles                       | pcicc104                            |

| 1.5                | PCI bus multi-data phase target abort cycles                             | pcicc105                            |

| 1.6                | PCI bus multi-data phase target retry cycles                             | pcicc106                            |

| 1.7                | PCI bus multi-data phase target disconnect cycles                        | pcicc107                            |

| 1.8                | PCI bus multi-data phase & trdyn cycles                                  | pcicc108                            |

| 1.9                | PCI bus data parity error single cycles                                  | pcicc109                            |

| 1.10               | PCI bus data parity error multi-data phase cycles                        | pcicc110                            |

| 1.11               | PCI bus master time-out                                                  | pcicc111                            |

| 1.13               | PCI bus master parking                                                   | pcicc113                            |

| 1.14               | PCI bus master arbitration                                               | pcicc114                            |

| 2.5                | Target ignores reserved commands (including dual address)                | pcicc205                            |

| 2.6                | Target reception of configuration cycles                                 | pcicc206                            |

| 2.8                | Target receives configuration cycles with address and data parity errors | pcicc208                            |

| 2.9                | Target receives memory cycles                                            | pcicc209                            |

| 2.10               | Target receives memory cycles with address and data parity errors        | pcicc210                            |

### Note:

(1) The file extension depends on the type of simulation file used, e.g., simulation channel file (**.scf**), vector file (**.vec**), or VHDL file.

# **PCI Bus Signals**

The following PCI bus signals are used by the pci\_a function:

- *Input*—Standard input-only signal.

- *Output*—Standard output-only signal.

- *Bidirectional*—Tri-state input/output signal.

- Sustained tri-state—Signal that is driven by one agent at a time (e.g., device or host operating on the PCI bus). An agent that drives a sustained tri-state pin low must actively drive it high for one clock cycle before tri-stating it. Another agent cannot drive a sustained tri-state signal any sooner than one clock cycle after it is released by the previous agent.

- Open-drain—Signal that is wire-ORed with other agents. The signaling agent asserts the open-drain signal, and a weak pull-up resistor deasserts the open-drain signal. The pull-up resistor may take two or three PCI bus clock cycles to restore the open-drain signal to its inactive state.

Table 2 summarizes the PCI bus signals interfacing the pci\_a to the PCI bus. See "Local Side Signals" on page 7 for information on local side signals.

|          |                                              | -        |                                                                                                                                                                                                                                             |

|----------|----------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name     | Туре                                         | Polarity | Description                                                                                                                                                                                                                                 |

| clk      | Input                                        | _        | Clock. The clk input provides the reference signal for all other PCI interface signals, except rstn and intan.                                                                                                                              |

| rstn     | Input                                        | Low      | Reset. The rstn input initializes the FLEX 10K PCI interface circuitry, and can be asserted asynchronously to the PCI bus clk edge. When active, the PCI output signals are tri-stated and the open-drain signals, such as serrn, float.    |

| gntn     | Input                                        | Low      | Grant. The gntn input indicates to the master device that it has control of the PCI bus. Every master device has a pair of arbitration lines (gntn and reqn) that connect directly to the arbiter.                                          |

| reqn     | Output                                       | Low      | Request. The reqn output indicates to the arbiter that the master wants to gain control of the PCI bus to perform a transaction.                                                                                                            |

| ad[310]  | Tri-State                                    | -        | Address/data bus. The ad[310] bus is a time-<br>multiplexed address/data bus; each bus transaction consists<br>of an address phase followed by one or more data phases.<br>The data phases occur when irdyn and trdyn are both<br>asserted. |

| cben[30] | Tri-State<br>Master: Output<br>Target: Input | Low      | Command/byte enable. The cben[30] bus is a time-<br>multiplexed command/byte enable bus. During the address<br>phase this bus indicates the command; during the data<br>phase this bus indicates byte enables.                              |

| par      | Tri-State                                    | _        | Parity. The par signal is a tri-stated output of even parity.<br>The number of 1s on ad[310], cben[30], and par is<br>an even number.                                                                                                       |

Table 2. PCI Signals Interfacing the pci\_a to the PCI Bus (Part 1 of 2)

| Name                      | Туре                                                      | Polarity | Description                                                                                                                                                                                                                                                                                                                                                                       |  |

|---------------------------|-----------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| framen<br><i>Note (1)</i> | Sustained<br>Tri-State<br>Master: Output<br>Target: Input | Low      | Frame. The framen is an output from the current bus master<br>that indicates the beginning and duration of a bus operation.<br>When framen is initially asserted, the address and<br>command signals are present on the ad[310] and<br>cben[30] buses. The framen signal remains asserted<br>during the data operation and is deasserted to identify the<br>end of a transaction. |  |

| irdyn                     | Sustained<br>Tri-State<br>Master: Output<br>Target: Input | Low      | Initiator ready. The irdyn signal is an output from a bus<br>master to its target and indicates that the bus master can<br>complete a data transaction. In a write transaction, irdyn<br>indicates that valid data is on the ad[310] bus. In a read<br>transaction, irdyn indicates that the master is ready to<br>accept the data on the ad[310] bus.                            |  |

| devseln                   | Sustained<br>Tri-State<br>Master: Input<br>Target: Output | Low      | Device select. Target asserts devseln to indicates that the target has decoded its own address.                                                                                                                                                                                                                                                                                   |  |

| trdyn<br><i>Note (1)</i>  | Sustained<br>Tri-State<br>Master: Input<br>Target: Output | Low      | Target ready. The trdyn is a target output, indicating that<br>the target can complete the current data transaction. In a<br>read operation, trdyn indicates that the target is providing<br>data on the ad[310] bus. In a write operation, trdyn<br>indicates that the target is ready to accept data on the<br>ad[310] bus.                                                     |  |

| stopn<br><i>Note (1)</i>  | Sustained<br>Tri-State<br>Master: Input<br>Target: Output | Low      | Stop. The stopn signal is a target device request that indicates to the bus master to stop the current transaction.                                                                                                                                                                                                                                                               |  |

| idsel                     | Input                                                     | High     | Initialization device select. The idsel input is a chip select for configuration read or write operations.                                                                                                                                                                                                                                                                        |  |

| perrn                     | Sustained<br>Tri-State                                    | Low      | Parity error. The perrn signal indicates a data parity error.                                                                                                                                                                                                                                                                                                                     |  |

| serrn                     | Open-Drain                                                | Low      | System error. The serrn signal indicates system error and address parity error.                                                                                                                                                                                                                                                                                                   |  |

| intan                     | Open-Drain                                                | Low      | Interrupt A. The intan signal is an active-low interrupt to the host, and must be used for any single-function device requiring an interrupt capability.                                                                                                                                                                                                                          |  |

#### Note:

Г

To allow the pci\_a to pass the PCI set-up time requirement, the framen, trdyn, and stopn signals are split into (1) two unidirectional (input, output) signals. For example, the PCI signal trdyn is connected to the input trdyn\_in and the output trdyn\_out. The input trdyn\_in is connected to a dedicated input on the FLEX 10K device, and the output trdyn\_out is connected to an I/O pin on the FLEX 10K device.

The PCI bus and FLEX 10K devices allow Joint Test Action Group (JTAG) boundary-scan testing (BST). To use JTAG BST, designers should connect the PCI bus JTAG pins with the FLEX 10K device JTAG pins. See Table 3.

| Table 3. Optional JTAG Signals |        |          |                                                                                                                   |  |  |

|--------------------------------|--------|----------|-------------------------------------------------------------------------------------------------------------------|--|--|

| Name                           | Туре   | Polarity | Description                                                                                                       |  |  |

| ТСК                            | Input  | High     | Test clock. The TCK input is used to clock test mode and test data in and out of the device.                      |  |  |

| TMS                            | Input  | High     | Test mode select. The TMS input is used to control the state of the test access port (TAP) control in the device. |  |  |

| TDI                            | Input  | High     | Test data. The TDI input is used to shift the test data and instruction into the device.                          |  |  |

| TDO                            | Output | High     | Test data. The TDO output is used to shift the test data and instruction out of the device.                       |  |  |

# **Local Side Signals**

Table 4 summarizes the pci\_a signals that interface the pci\_a to the local side peripheral device(s).

| Table 4. pci_a Signals Interfacing the pci_a to the Local Side (Part 1 of 3) |       |          |                                                                                                                                                                                                                                                                        |  |  |

|------------------------------------------------------------------------------|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Name                                                                         | Туре  | Polarity | Description                                                                                                                                                                                                                                                            |  |  |

| l_irqn                                                                       | Input | Low      | Local side interrupt request. The local side peripheral<br>device asserts 1_irqn to signal a PCI bus interrupt.<br>For example, when the local side peripheral device<br>requires a DMA transfer, it could use the 1_irqn<br>input to request servicing from the host. |  |  |

| l_holdn                                                                      | Input | Low      | Local hold. When asserted, 1_holdn suspends the current DMA transfer. As long as 1_holdn is active, data transfers cannot occur between the pci_a and the local side peripheral device.                                                                                |  |  |

| l_req                                                                        | Input | High     | Local DMA request. The local side peripheral device<br>asserts 1_req, which signals the pci_a to request<br>permission for a PCI DMA operation.                                                                                                                        |  |  |

| l_dat_in[310]                                                                | Input | _        | Local data bus input. The l_dat_in[310] input is<br>driven active by the local side peripheral device during<br>pci_a-initiated DMA write transactions (i.e., local<br>side DMA read transactions) and PCI bus target read<br>transactions.                            |  |  |

| Name       | Туре   | Polarity | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| l_adr[180] | Output | _        | Local target address. The 1_adr[180] output<br>represents the 128K DWORDS of target register<br>space available to the local side peripheral device.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| l_csn      | Output | Low      | Local target chip select. When active, 1_csn notifies<br>the peripheral device of an impending target<br>transaction. Any PCI master device can read or write<br>to a local side peripheral device through the pci_a.<br>The 1_ackn and the 1_csn outputs are never<br>asserted at the same time.                                                                                                                                                                                                                                                                                   |

| 1_rdn      | Output | Low      | Read. The pci_a asserts l_rdn to signal a read<br>access to the local side peripheral device. The pci_a<br>uses the l_rdn for reading from peripheral device<br>target registers and for PCI DMA write transactions. A<br>PCI DMA write transaction begins when the pci_a<br>reads data from the peripheral device. For target read<br>operations, the pci_a asserts the l_csn and l_rdn<br>signals. For DMA read operations, the pci_a asserts<br>the l_ackn and l_rdn signals.                                                                                                    |

| l_wrn      | Output | Low      | Write. The pci_a asserts l_wrn to signal a write<br>access to the local side peripheral device. The pci_a<br>uses the l_wrn output for writing to peripheral device<br>target registers and for PCI DMA read transactions. A<br>PCI DMA read operation begins when the pci_a<br>reads data from memory over the PCI bus and into the<br>internal EAB RAM buffer, and then writes the data out<br>to the peripheral device. For a write operation, the<br>pci_a also asserts either l_csn for target accesses<br>to the local side, or l_ackn for DMA accesses to the<br>local side. |

| l_ackn     | Output | Low      | Local DMA acknowledge. When low, 1_ackn notifies<br>the local side peripheral device that it has been<br>granted a DMA read or write transaction. The<br>peripheral device can then transfer data to or from the<br>PCI bus through the pci_a.                                                                                                                                                                                                                                                                                                                                      |

Table 4. pci\_a Signals Interfacing the pci\_a to the Local Side (Part 2 of 3)

| Name           | Туре   | Polarity | Description                                                                                                                                                                                                                                        |

|----------------|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| l_clk          | Output | -        | Local PCI clock. The l_clk is a buffered version of<br>the PCI bus clock and is used by the local side<br>peripheral device to synchronize all control logic to the<br>pci_a.                                                                      |

| l_reset        | Output | High     | Local reset. The pci_a asserts the l_reset output<br>to reset the local side peripheral device. The<br>l_reset output is active during a PCI master reset<br>and follows the state of the l_rst bit (bit 2 of the DMA<br>control status register). |

| 1_dat_out[310] | Output | -        | Local data bus output. The pci_a drives the<br>l_dat_out[310] output during pci_a-initiated<br>DMA read transactions (i.e., local side DMA write<br>transactions) and PCI target write transactions.                                               |

# **Function Prototype**

The Altera Hardware Description Language (AHDL<sup>™</sup>) Function Prototype of the pci\_a is shown below:

```

FUNCTION pci_a (clk, framen_in, gntn, idsel,

l_dat_in[31..0], l_holdn, l_irqn, l_req, rstn,

stopn_in, trdyn_in)

WITH (SUBSYSTEM_ID, SUBSYSTEM_VEND_ID, DEVICE_ID,

DEVICE_VEND_ID, CLASS_CODE, REVISION_ID)

RETURNS (framen_out, l_ackn, l_adr[18..0], l_clk,

l_csn, l_dat_out[31..0], l_ rdn, l_reset, l_wrn,

stopn_out, trdyn_out, ad[31..0], cben[3..0], devseln,

intan, irdyn, par, perrn, reqn, serrn);

```

# **Parameters**

The pci\_a parameters set read-only PCI bus configuration registers in the pci\_a; these registers are called device identification registers. See "Configuration Registers" on page 15 for more information on device ID registers. Table 5 describes the parameters of the pci\_a function.

| Table 5. Parameters |                        |                                |                              |  |  |

|---------------------|------------------------|--------------------------------|------------------------------|--|--|

| Name                | Value<br>(Hexadecimal) | Default Value<br>(Hexadecimal) | Description                  |  |  |

| CLASS_CODE          | 24-bit                 | FF0000                         | Class code register          |  |  |

| DEVICE_ID           | 16-bit                 | 0001                           | Device ID register           |  |  |

| DEVICE_VEND_ID      | 16-bit                 | 1172                           | Device vendor ID register    |  |  |

| REVISION_ID         | 8-bit                  | 01                             | Revision ID register         |  |  |

| SUBSYSTEM_ID        | 16-bit                 | 0000                           | Subsystem ID register        |  |  |

| SUBSYSTEM_VEND_ID   | 16-bit                 | 0000                           | Subsystem vendor ID register |  |  |

# Functional Description

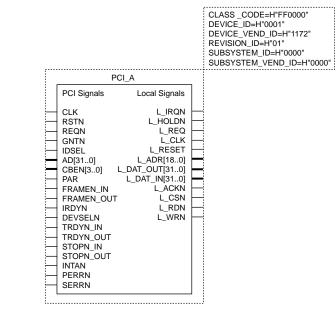

The pci\_a function consists of three main components:

- A defined 64-byte PCI bus configuration register space and master control logic

- PCI bus target interface control logic, including target decode and register read/write signals

- Embedded DMA control engine, which operates with four registers and includes a 64-byte (16 DWORD) RAM buffer, and local side interface DMA control logic, including read/write control and PCI bus arbitration for master/target accesses

Figure 2 shows the pci\_a block diagram.

Figure 2. pci\_a Block Diagram

# **Sustained Tri-State Signal Operation**

The PCI specification defines signals that are constantly sampled by different bus agents yet driven by one agent at a time, as sustained tristate signals. For example, framen is constantly sampled by different PCI bus targets (to detect the start of a transaction), and yet driven by one PCI bus master at a time.

For sustained tri-state signals, the PCI specification requires using one clock cycle to drive the signals inactive before being tri-stated. The PCI specification also requires that any sustained tri-state signal being released, such as the master device releasing ad[31..0] after asserting the address on a read operation, be given a full clock cycle to tri-state before another device can drive it.

The PCI specification defines a turn-around cycle as the clock cycle where a sustained tri-state signal is being tri-stated so that another bus agent can drive it. Turn-around cycles prevent contention on the bus.

# **Master Device Signals & Signal Assertion**

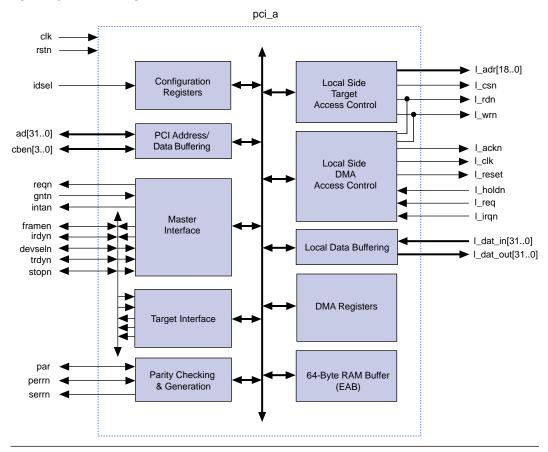

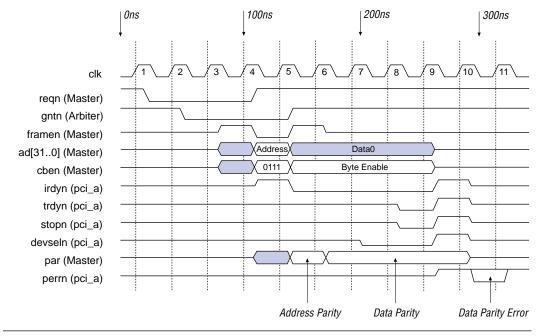

Figure 3 illustrates the PCI-compliant master device signals interfacing the pci\_a with the PCI bus. The signals are grouped by functionality, and signal directions are illustrated from the perspective of the pci\_a operating as a master on the PCI bus.

A pci\_a master sequence begins with the assertion of reqn to request mastership of the PCI bus. After receiving gntn from the arbiter (usually the PCI host bridge) and after the bus idle state is detected, the pci\_a initiates the address phase by asserting framen and driving both the PCI address on ad[31..0] and the bus command on cben[3..0]for one clock cycle.

When the pci\_a is ready to present data on the bus, it asserts irdyn. At this point, the pci\_a master logic monitors the control signals driven by the target device. (A target device is determined by the decoding of the address and command signals presented on the PCI bus during the address phase of the transaction.) The target device drives the control signals devseln, trdyn, and stopn to indicate one of the following:

- The data transaction has been decoded and accepted.

- The target device is ready for the data operation. (When both trdyn and irdyn are active, a data word is clocked from the sending to the receiving device.)

- The master device should stop the current transaction.

Figure 3. pci\_a Master Device Signals

# **Target Device Signals & Signal Assertion**

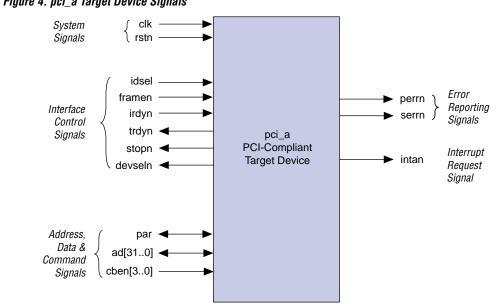

Figure 4 illustrates the PCI-compliant target device signals interfacing the pci\_a with the PCI bus. The signals are grouped by functionality, and signal directions are illustrated from the perspective of the pci\_a operating as a target on the PCI bus.

A pci\_a target sequence begins when the master device asserts framen and drives the address of the target and the command on the PCI bus. When the target device decodes its address on the PCI bus, it asserts devseln to indicate to the master that it has accepted the transaction. The master will then assert irdyn to indicate to the target device that:

- For a read operation, the master device can complete a data transaction.

- For a write operation, valid data is on the ad[31..0] bus.

When the pci\_a functions as the selected target device, it will drive the control signals devseln, trdyn, and stopn as discussed in "Master Device Signals & Signal Assertion" on page 12.

As a target device, the pci\_a only supports single-cycle accesses; therefore, the pci\_a simultaneously drives stopn and trdyn active. When qualified by an active irdyn signal, a data word is clocked from the sending to the receiving device.

### Figure 4. pci\_a Target Device Signals

### **Parity Signal Operation**

All bus cycles include parity. Every device that transmits on the ad[31..0] bus must also drive the par signal, including master devices outputting the address. Because parity on the PCI bus is even, the number of logic 1s on ad[31..0], cben[3..0], and par must be even. Parity checking is not required, but can be enabled through the agent's PCI command register. Address parity errors are presented on the serrn output, and data parity errors are presented on the perrn output. The par bit lags the ad[31..0] bus by one clock cycle, and parity error signals lag the par bit by one clock cycle; thus, parity error signals lag the address or data by two clock cycles.

# **Bus Master Commands**

When the pci\_a acquires mastership of the PCI bus, it can initiate a memory read or memory write command. During the address phase of a transaction, the cben[3..0] bus is used to indicate the transaction type. See Table 6.

The pci\_a supports memory read/write and configuration read/write commands. When operating as a master device, the pci\_a executes standard memory read and write operations. When operating as a target, the pci\_a responds to standard memory read and write transactions. The pci\_a also responds to configuration read and write operations.

Table 6 summarizes the PCI bus commands that are supported by the pci\_a.

| Table 6. PCI Bus Command Support Summary |                     |                |                |  |  |

|------------------------------------------|---------------------|----------------|----------------|--|--|

| cben[30] Value                           | Bus Command Cycle   | Target Support | Master Support |  |  |

| 0110                                     | Memory read         | Yes            | Yes            |  |  |

| 0111                                     | Memory write        | Yes            | Yes            |  |  |

| 1010                                     | Configuration read  | Yes            | No             |  |  |

| 1011                                     | Configuration write | Yes            | No             |  |  |

# Configuration Registers

Each logical PCI bus device includes a block of 64 configuration DWORDS reserved for the implementation of its configuration registers. The format of the first 16 DWORDS is defined by the PCI SIG's **PCI Local Bus** *Specification* compliance checklist, revision 2.1, which defines two header formats, type one and type zero. Header type one is used for PCI-to-PCI bridges; header type zero is used for all other devices, including the pci\_a.

Table 7 displays the defined 64-byte configuration space. The registers within this range are used to identify the device, control PCI bus functions, and provide PCI bus status. The shaded areas indicate registers that are supported by the pci\_a.

| Address | Byte                                |               |               |                 |  |  |

|---------|-------------------------------------|---------------|---------------|-----------------|--|--|

|         | 3                                   | 2             | 1             | 0               |  |  |

| 00H     | Devi                                | ce ID         | Venc          | lor ID          |  |  |

| 04H     | Status I                            | Register      | Command       | d Register      |  |  |

| 08H     |                                     | Class Code    |               | Revision ID     |  |  |

| 0CH     | BIST                                | Header Type   | Latency Timer | Cache Line Size |  |  |

| 10H     |                                     | Base Addres   | ss Register 0 |                 |  |  |

| 14H     |                                     | Base Addres   | ss Register 1 |                 |  |  |

| 18H     | Base Address Register 2             |               |               |                 |  |  |

| 1CH     | Base Address Register 3             |               |               |                 |  |  |

| 20H     |                                     | Base Addres   | ss Register 4 |                 |  |  |

| 24H     |                                     | Base Addres   | ss Register 5 |                 |  |  |

| 28H     |                                     | Card Bus      | CIS Pointer   |                 |  |  |

| 2CH     | Subsystem ID Subsystem Vendor ID    |               |               |                 |  |  |

| 30H     | Expansion ROM Base Address Register |               |               |                 |  |  |

| 34H     | Reserved                            |               |               |                 |  |  |

| 38H     | Reserved                            |               |               |                 |  |  |

| 3CH     | Maximum<br>Latency                  | Minimum Grant | Interrupt Pin | Interrupt Line  |  |  |

Table 8 summarizes the pci\_a-supported configuration registers address map. Read/write refers to the status at run time, i.e., from the perspective of other PCI bus agents. Designers can set some of the read-only registers at design time by setting the parameters when the pci\_a is instantiated in MAX+PLUS II. For example, the device ID register value can be modified from its default value by changing the DEVICE\_ID parameter in MAX+PLUS II. The specified default state is defined as the state of the register when the PCI bus is reset.

| Table 8. pci_a-Supported Configuration Registers Address Map |                                    |                         |            |            |                            |  |

|--------------------------------------------------------------|------------------------------------|-------------------------|------------|------------|----------------------------|--|

| Address Offset<br>(Hexadecimal)                              | Range<br>Reserved<br>(Hexadecimal) | Bytes Used/<br>Reserved | Read/Write | Mnemonic   | Register Name              |  |

| 00                                                           | 00-01                              | 2/2                     | Read       | ven_id     | Vendor ID                  |  |

| 02                                                           | 02-03                              | 2/2                     | Read       | dev_id     | Device ID                  |  |

| 04                                                           | 04-05                              | 2/2                     | Read/Write | comd       | Command                    |  |

| 06                                                           | 06-07                              | 2/2                     | Read/Write | status     | Status                     |  |

| 08                                                           | 08-08                              | 1/1                     | Read       | rev_id     | Revision ID                |  |

| 09                                                           | 09-0B                              | 3/3                     | Read       | class      | Class code                 |  |

| 0D                                                           | 0D-0D                              | 1/1                     | Read/Write | lat_tmr    | Latency timer              |  |

| 0E                                                           | 0E-0E                              | 1/1                     | Read       | header     | Header type                |  |

| 10                                                           | 10-13                              | 4/4                     | Read/Write | bar0       | Base address register zero |  |

| 2C                                                           | 2C-2D                              | 2/2                     | Read       | sub_ven_id | Subsystem vendor ID        |  |

| 2E                                                           | 2E-2F                              | 2/2                     | Read       | sub_id     | Subsystem ID               |  |

| 3C                                                           | 3C-3C                              | 1/1                     | Read/Write | int_ln     | Interrupt line             |  |

| 3D                                                           | 3D-3D                              | 1/1                     | Read       | int_pin    | Interrupt pin              |  |

| 3E                                                           | 3E-3E                              | 1/1                     | Read       | min_gnt    | Minimum grant              |  |

| 3F                                                           | 3F-3F                              | 1/1                     | Read       | max_lat    | Maximum latency            |  |

# Vendor ID Register (Offset = 00 Hex)

Vendor ID is a 16-bit read-only register that identifies the manufacturer of the device (e.g., Altera for the pci\_a). The value of this register is assigned by the PCI SIG; the default value of this register is the Altera vendor ID value, which is 1172 hex. However, by setting the DEVICE\_VEND parameter (see Table 5), designers can change the value of the vendor ID register to their PCI SIG-assigned vendor ID value. See Table 9.

| Table 9. Vendor ID Register Format      |        |      |               |  |

|-----------------------------------------|--------|------|---------------|--|

| Data Bit Mnemonic Read/Write Definition |        |      |               |  |

| 150                                     | ven_id | Read | PCI vendor ID |  |

# Device ID Register (Offset = 02 Hex)

Device ID is a 16-bit read-only register that identifies the type of device. The value of this register is assigned by the manufacturer (e.g., Altera assigned the value of the device ID register for the pci\_a). The default value of the device ID register is 0001 hex; however, designers can change the value of the device ID register by setting the parameter DEVICE\_ID (see Table 5).

# Command Register (Offset = 04 Hex)

Command is a 16-bit read and write register that provides basic control over the ability of the pci\_a to respond to and/or perform PCI bus accesses. See Table 10.

| Table 10. Command Register Format |          |            |                                                                                                                                                                                                                                                                                                            |  |

|-----------------------------------|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Data Bit                          | Mnemonic | Read/Write | Definition                                                                                                                                                                                                                                                                                                 |  |

| 0                                 | Unused   | -          | -                                                                                                                                                                                                                                                                                                          |  |

| 1                                 | mem_ena  | Read/Write | Memory access enable. When high, mem_ena enables<br>the pci_a to respond to the PCI bus memory<br>accesses as a target. Because the DMA registers are<br>set via memory target accesses, the mem_ena bit must<br>be set as part of the initialization operation for the<br>pci_a to perform DMA transfers. |  |

| 2                                 | mstr_ena | Read/Write | Master enable. When high, mstr_ena enables the pci_a to acquire mastership of the PCI bus. For the pci_a to perform DMA transfers, the mstr_ena bit must be set as a part of the initialization operation.                                                                                                 |  |

| 53                                | Unused   | -          | -                                                                                                                                                                                                                                                                                                          |  |

| 6                                 | perr_ena | Read/Write | Parity error enable. When high, perr_ena enables the pci_a to report parity errors via the perrn output.                                                                                                                                                                                                   |  |

| 7                                 | Unused   | -          | _                                                                                                                                                                                                                                                                                                          |  |

| 8                                 | serr_ena |            | System error enable. When high, serr_ena enables<br>the pci_a to report address parity errors via the<br>serrn output. However, to signal a system error, the<br>perr_ena bit must also be high.                                                                                                           |  |

| 159                               | Unused   | -          | -                                                                                                                                                                                                                                                                                                          |  |

# Status Register: (Offset = 06 Hex)

Status is a 16-bit register that provides the status of bus-related events. Read transactions to the status register behave normally. However, write transactions are different from typical write transactions in that bits in the status register can be cleared but not set. A bit in the status register is cleared by writing a logic one to that bit. For example, writing the value 4000 hex to the status register clears bit number 14 and leaves the rest of the bits unchanged. The default value of the status register is 0400 hex. See Table 11.

| Data Bit | Mnemonic    | Read/Write | Definition                                                                                                                                                                                                                                                                                                                              |

|----------|-------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 70       | Unused      | -          | -                                                                                                                                                                                                                                                                                                                                       |

| 8        | dat_par_rep | Read/Write | Data parity reported. When high, dat_par_rep<br>indicates that during a read transaction the pci_a<br>asserted the perrn output as a master device, or that<br>during a write transaction the perrn was asserted by<br>a target device. This bit is high only when the<br>perr_ena bit (bit 6 of the command register) is also<br>high. |

| 109      | devsel_tim  | Read       | Device select timing. The devsel_tim bits indicate target access timing of the pci_a via the devseln output. The pci_a is designed to be a slow target device.                                                                                                                                                                          |

| 11       | Unused      | -          | -                                                                                                                                                                                                                                                                                                                                       |

| 12       | tar_abrt    | Read/Write | Target abort. When high, tar_abrt indicates that the current target device transaction has been terminated                                                                                                                                                                                                                              |

| 13       | mstr_abrt   | Read/Write | Master abort. When high, mstr_abrt indicates that the current master device transaction has been terminated.                                                                                                                                                                                                                            |

| 14       | serr_set    | Read/Write | Signaled system error. When high, serr_set<br>indicates that the pci_a drove the serrn output<br>active, i.e., an address phase parity error has<br>occurred.                                                                                                                                                                           |

| 15       | det_par_err | Read/Write | Detected parity error. When high, det_par_err<br>indicates that the pci_a detected either an address or<br>data parity error. Even if parity error reporting is<br>disabled (via perr_ena), the pci_a will set the<br>det_par_err bit.                                                                                                  |

### Table 11. Status Register Format

# **Revision ID Register (Offset = 08 Hex)**

Revision ID is an 8-bit read-only register that identifies the revision number of the device. The value of this register is assigned by the manufacturer (e.g., Altera for the pci\_a). Therefore, the default value of the revision ID register is set as the revision number of the pci\_a. See Table 12. However, designers can change the value of the revision ID register by setting the REVISION\_ID parameter (see Table 5).

| Table 12. Revision ID Register Format   |        |      |                 |  |

|-----------------------------------------|--------|------|-----------------|--|

| Data Bit Mnemonic Read/Write Definition |        |      |                 |  |

| 70                                      | rev_id | Read | PCI revision ID |  |

# Class Code Register (Offset = 09 Hex)

Class code is a 24-bit read-only register divided into three sub-registers: base class, sub-class, and programming interface. Refer to the *PCI Local Bus Specification*, rev. 2.1 for detailed bit information. See Table 13. The default value of the class code register is FF0000 hex; however, designers can change the value by setting the CLASS\_CODE parameter (see Table 5).

| Table 13. Class Code Register Format    |       |      |            |  |

|-----------------------------------------|-------|------|------------|--|

| Data Bit Mnemonic Read/Write Definition |       |      |            |  |

| 230                                     | class | Read | Class code |  |

# Latency Timer Register (Offset = 0D Hex)

The latency timer register is an 8-bit register with bits 2, 1, and 0 tied to GND. The register defines the maximum amount of time, in PCI bus clock cycles, that the pci\_a can retain ownership of the PCI bus. After initiating a transaction, the pci\_a decrements its latency timer by one on the rising edge of each clock. The default value of the latency timer register is 00 hex. See Table 14.

| Table 14. Latency Timer Register Format |         |            |                        |  |

|-----------------------------------------|---------|------------|------------------------|--|

| Data Bit Mnemonic Read/Write Definition |         |            |                        |  |

| 20                                      | lat_tmr | Read       | Latency timer register |  |

| 73                                      | lat_tmr | Read/Write | Latency timer register |  |

# Header Type Register (Offset = OE Hex)

Header type is an 8-bit read-only register that identifies the pci\_a as a single-function device. The default value of the header type register is 00 hex. See Table 15.

| Table 15. Header Type Register Format   |                                |  |  |  |  |

|-----------------------------------------|--------------------------------|--|--|--|--|

| Data Bit Mnemonic Read/Write Definition |                                |  |  |  |  |

| 70                                      | 70 header Read PCI header type |  |  |  |  |

# Base Address Register Zero (Offset = 10 Hex)

Base address register zero (BAR0) consists of a 12-bit register (bits 31 through 20) that determines the base memory address of the pci\_a target space. The default value of the base address register is 0000.0000 hex. See Table 16.

| Table 16. Base | Table 16. Base Address Register Format |            |                                                                                                                                                                                                                                              |  |  |  |

|----------------|----------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Data Bit       | Mnemonic                               | Read/Write | Definition                                                                                                                                                                                                                                   |  |  |  |

| 0              | mem_ind                                | Read       | Memory indicator. The mem_ind bit indicates whether<br>the register is I/O or a memory address decoder. In the<br>pci_a, the mem_ind bit is tied to GND, which indicates<br>a memory address decoder.                                        |  |  |  |

| 21             | mem_type                               | Read       | Memory type. The mem_type bits indicate the type of memory that can be implemented in the pci_a memory address space. These bits are tied to GND, which indicates that the memory block can be located anywhere in the 32-bit address space. |  |  |  |

| 3              | pre_fetch                              | Read       | Memory prefetchable. The pre_fetch bit indicates<br>whether the block of memory defined by BAR0 is<br>prefetchable by the host bridge. In the pci_a, the<br>address space is not prefetchable, i.e., it reads as low.                        |  |  |  |

| 194            | Unused                                 | -          | _                                                                                                                                                                                                                                            |  |  |  |

| 3120           | bar0                                   | Read/write | Base address register 0.                                                                                                                                                                                                                     |  |  |  |

# Subsystem Vendor ID Register (Offset = 2C Hex)

Subsystem vendor ID is a 16-bit read-only register that identifies add-in cards designed by different vendors but with the same functional device on the card. The value of this register is assigned by the PCI SIG. See Table 17. The default value of the subsystem vendor ID register is 0000 hex; however, designers can change the value by setting the SUBSYSTEM\_VEND\_ID parameter (see Table 5).

| Table 17. Subsystem Vendor ID Register Format |             |      |                         |  |

|-----------------------------------------------|-------------|------|-------------------------|--|

| Data Bit Mnemonic Read/Write Definition       |             |      |                         |  |

| 150                                           | sub_vend_id | Read | PCI subsystem/vendor ID |  |

# Subsystem ID Register (Offset = 2E Hex)

Subsystem ID register identifies the subsystem; the value of this register is defined by the subsystem vendor, i.e., the designer. See Table 18. The default value of the subsystem ID register is 0000 hex; however, designers can change the value by setting the SUBSYSTEM\_ID parameter (see Table 5).

| Table 18. Subsystem ID Register Format  |        |      |                  |  |  |

|-----------------------------------------|--------|------|------------------|--|--|

| Data Bit Mnemonic Read/Write Definition |        |      |                  |  |  |

| 150                                     | sub_id | Read | PCI subsystem ID |  |  |

# Interrupt Line Register (Offset = 3C Hex)

The interrupt line register consists of an 8-bit register that defines to which system interrupt request line (on the system interrupt controller) the intan output is routed. The interrupt line register is written to by the system software on power-up; the default value is FF hex. See Table 19.

| Table 19. Interrupt Line Register Format |        |            |                         |  |

|------------------------------------------|--------|------------|-------------------------|--|

| Data Bit Mnemonic Read/Write Definition  |        |            |                         |  |

| 70                                       | int_ln | Read/write | Interrupt line register |  |

# Interrupt Pin Register (Offset = 3D Hex)

The interrupt pin register consists of an 8-bit read-only register that defines the pci\_a PCI bus interrupt request line to be intan. The default value of the interrupt pin register is 01 hex. See Table 20.

| Table 20. Interrupt Pin Register Format |         |      |                        |  |

|-----------------------------------------|---------|------|------------------------|--|

| Data Bit Mnemonic Read/Write Definition |         |      |                        |  |

| 70                                      | int_pin | Read | Interrupt pin register |  |

# Minimum Grant Register (Offset = 3E Hex)

Minimum grant register consists of an 8-bit read-only register that defines the length of time the pci\_a would like to retain mastership of the PCI bus. The value set in this register indicates the required burst period length in 250-ns increments. The pci\_a requests a timeslice of 4 microseconds. The default state of the minimum grant register is 10 hex. See Table 21.

| Table 21. Minimum Grant Register Format |          |            |                        |  |

|-----------------------------------------|----------|------------|------------------------|--|

| Data Bit                                | Mnemonic | Read/Write | Definition             |  |

| 70                                      | min_gnt  | Read       | Minimum grant register |  |

# Maximum Latency Register (Offset = 3F Hex)

The maximum latency register is an 8-bit read-only register that defines the frequency in which the pci\_a would like to gain access to the PCI bus. The value of the maximum latency register is set to 00 hex, which indicates that the pci\_a has no major requirements for maximum latency. See Table 22.

| Table 22. Maximum Latency Register Format |          |            |                          |  |

|-------------------------------------------|----------|------------|--------------------------|--|

| Data Bit                                  | Mnemonic | Read/Write | Definition               |  |

| 70                                        | max_lat  | Read       | Maximum latency register |  |

# PCI Bus Transactions

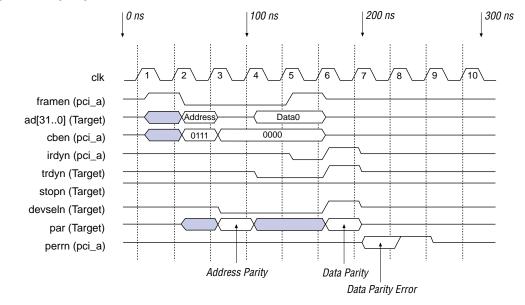

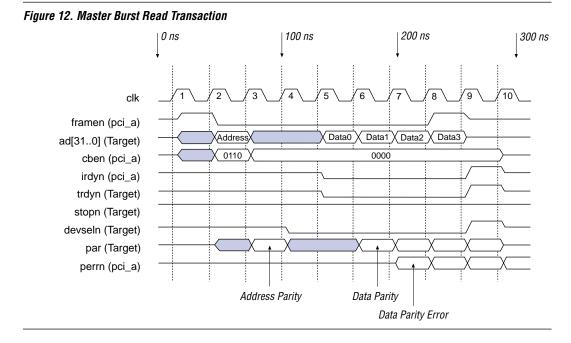

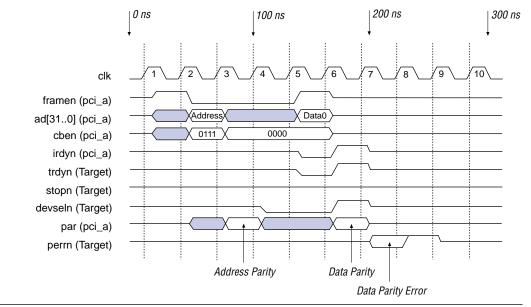

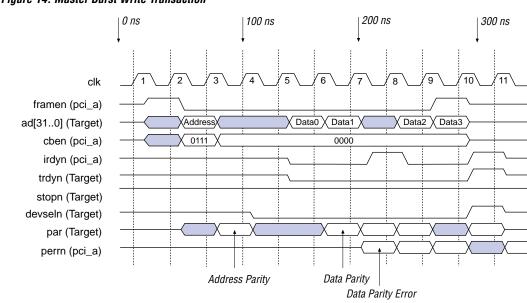

This section describes pci\_a PCI bus transactions. The following should be considered when reading the diagrams in this section:

- All pci\_a accesses to the PCI bus are quad-byte, or 32-bit transfers; therefore, all byte enables are active for the duration of data transfers.

- Although Figures 5 through 14 show PCI bus signals as tri-stated when not driven by the pci\_a, they are actually high due to the pullup resistors used to keep sustained tri-state signals at a logic high while the signals are not being driven by a PCI bus agent.

The pci\_a accesses the PCI bus for three types of transactions:

- Target

- Device configuration

- Master

# **Target Transactions**

A target read or write transaction begins after the master acquires mastership of the PCI bus and asserts framen to indicate the beginning of a bus transaction. The pci\_a latches the address and command signals on the first clock edge when framen is asserted and starts the address decode phase.

# Target Read Transactions

The pci\_a supports two types of target read transactions:

- Internal target read—Target read transaction from the internal DMA registers

- *External target read*—Target read transaction from the local side target memory space

The sequence of events in both target read transactions is identical; however, the timing is not. A target read transaction from the local side target memory space requires more time because the pci\_a must wait for the local side to supply it with data.

### **Internal Target Read Transaction**

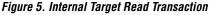

Immediately after the address phase (clock 4), the master deasserts framen and asserts irdyn, indicating both of the following:

- The transaction contains a single data phase.

- The master device is ready to read the data that the pci\_a has presented on the ad[31..0] bus.

The master device tri-states the ad[31..0]bus in clock five after the pci\_a latches the address. The pci\_a can drive the ad[31..0] bus beginning in clock six. If the master is attempting a burst access, it will keep both framen and irdyn signals asserted. However, because the pci\_a does not support target bursts, it will assert stopn to indicate a disconnect to the master. The master will subsequently end the transaction by deasserting framen and asserting irdyn for one clock cycle.

In Figure 5, the pci\_a asserts devseln in clock seven, which indicates to the master device that the pci\_a has accepted the transaction. The devseln is then sampled by the master device on the rising-edge of clock eight, which is slow decode timing. The pci\_a is a slow decode device during target and configuration read or write transactions. Figure 5 shows the timing of a pci\_a internal target read transaction.

In Figure 5, the pci\_a asserts trdyn and stopn in clock eight to indicate that valid data is on the ad[31..0] bus and a disconnect is desired. Data is transferred during clock eight when irdyn and trdyn are active and latched by the master device on the rising-edge of clock nine. In the case of an attempted burst transfer, the PCI specification requires that a target device that does not support burst transfers must issue a disconnect during the first data phase. Because of the PCI specification, the pci\_a always asserts stopn and trdyn at the same time.

The master drives the par active in clock five for address parity, and the pci\_a drives par active in clock nine for data parity. In a target read transaction, the master device drives the perrn signal to indicate data parity errors.

In clock nine, because the data has been sampled, the pci\_a releases the ad[31..0]bus and the master releases cben[3..0]. The devseln, trdyn, and stopn signals are driven high in clock nine and released by the pci\_a one clock later. Thus, the sustained tri-state signal requirement is met, i.e., driving the signal high for one clock cycle before releasing it.

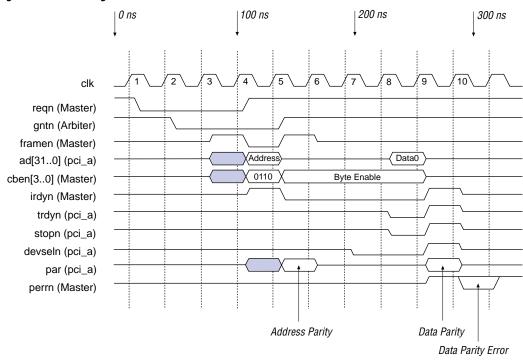

### **External Target Read Transaction**

Again, the sequence of events in an external target read transaction is identical to an internal target read transaction. However, because the pci\_a must wait for the local side to supply it with data, a target read transaction from the local side target memory space requires more time. Also, because a DMA access to the local side takes precedence over any other access to the local side, an external target read transaction is allowed to complete only when the DMA is in an idle state. If an external target read transaction is received by the pci\_a while the DMA is not in an idle state, the pci\_a signals a retry.

Figures 6 shows the timing of a pci\_a external target read transaction.

#### Figure 6. External Target Read Transaction

### Target Write Transactions

The pci\_a supports two types of target write transactions:

- Internal target write: Target write to internal DMA registers

- External target write: Target write to the local side target memory space

The sequence of events in both target write transactions is identical; however, the timing may not be.

### **Internal Target Write Transaction**

Immediately after the address phase, the master deasserts framen and asserts irdyn, indicating the following:

- The transaction contains a single data phase.

- The master device is ready to write data on the ad[31..0]bus for the target device to receive.

If the master device is not ready for the data phase to begin, irdyn is delayed and framen is not deasserted until the clock where irdyn goes active. If the master is attempting a burst access, it will keep both framen and irdyn signals asserted. However, because the pci\_a does not support target bursts, it will assert stopn to indicate a disconnect to the master. The master will subsequently end the transaction by deasserting framen and asserting irdyn for one clock cycle.

In Figure 7, the pci\_a asserts devseln in clock seven, which indicates to the master device that the pci\_a has accepted the transaction. The devseln signal is then sampled by the master device on the rising edge of clock eight, which is slow decode timing.

In Figure 7, where the data phase occurs in clocks five through eight, the master device drives data on the ad[31..0] bus simultaneously with the assertion of irdyn in clock five. To indicate completion of the data phase and to request a bus disconnect, the pci\_a asserts trdyn and stopn in clock eight. Data is transferred during clock eight when irdyn and trdyn are active, and latched by the pci\_a on the rising edge of clock nine. In the case of an attempted burst write transfer, the PCI specification requires that a target device that does not support burst transfers must issue a disconnect during the first data phase. Because of the PCI specification, the pci\_a always asserts stopn and trdyn at the same time.

The master device drives par active in clock five for parity of the address bits, and clock six for parity of the data bits. In a target write transaction, the pci\_a drives perrn to indicate data parity errors.

In clock nine, because the data has been sampled, the pci\_a releases the ad[31..0] and cben[3..0] buses. One clock later par is released by the master device and devseln, trdyn, and stopn are release by the pci\_a. The devseln, trdyn, and stopn are driven high in clock nine and released one clock later. Figure 7 shows the timing of an internal target write transaction.

Figure 7. Internal Target Write Transaction

### **External Target Write Transaction**

Again, the sequence of events in an external target write transaction is identical to an internal target write transaction. However, the timing may be different.

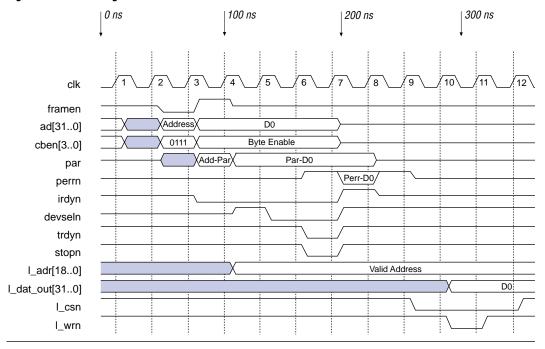

To allow an external target write transaction to complete faster, the pci\_a provides a single address and a single data holding register. When an external target write access takes place, the pci\_a stores the address and data in its internal holding registers and completes the transfer on the PCI bus. The pci\_a will subsequently assert its l\_csn signal to indicate to the local side that there is a pending target access; once clock later (clock 10), the l\_wrn and l\_dat\_out signals are also asserted. Figure 8 shows the timing of an external target write transaction.

#### Figure 8. External Target Write Transaction

# **Configuration Transactions**

A configuration transaction is generated by either a host-to-PCI bridge or PCI-to-PCI bridge access. In the address phase of a configuration transaction, the PCI bridge will drive the idsel signal of the PCI bus agent that it wants to access. If a PCI bus agent decodes the configuration command and detects its idsel to be high, the agent will claim the configuration access and assert devsel.

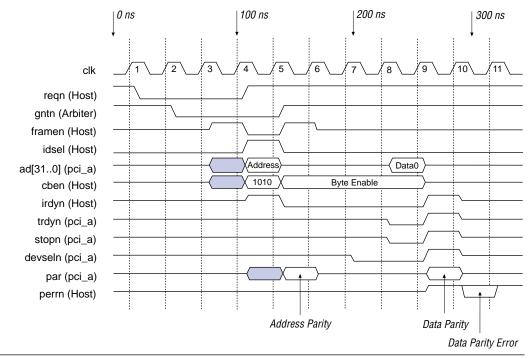

### PCI Configuration Read Transaction

Figure 9 shows the timing of a pci\_a configuration read transaction. The protocol is identical to the protocol discussed in the "Target Read Transactions" on page 24 except for the idsel signal, which is active during the address phase of a configuration transaction.

Figure 9. Configuration Read Transaction

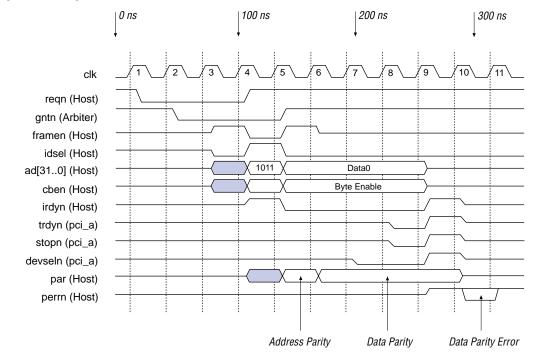

# PCI Configuration Write Transaction

Figure 10 shows the timing of a pci\_a configuration write transaction. The protocol is identical to the protocol discussed in the "Target Write Transactions" on page 27 except for the idsel signal, which is active during the address phase of a configuration transactions.

### Figure 10. Configuration Write Transaction

### **Master Transactions**

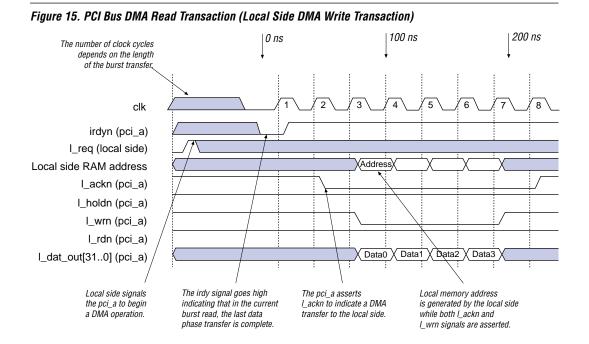

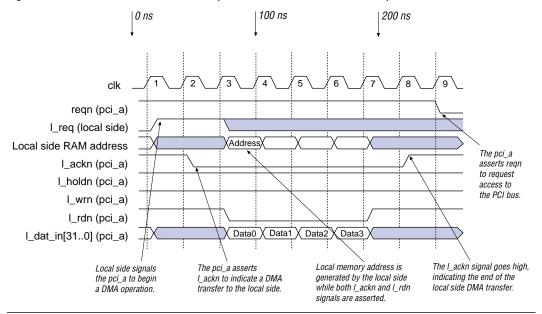

Master transactions in the pci\_a are controlled by the DMA engine. A pci\_a master transaction begins after the user loads the appropriate values in the DMA register (see "General Programming Guidelines" on page 47 for more detailed information on DMA register loading). The pci\_a waits for the local side to assert l\_req, which indicates to the pci\_a that it can begin the DMA operation.

In a DMA read (PCI to local side) transaction, the pci\_a immediately asserts reqn to acquire mastership of the PCI bus. After the arbiter asserts gntn, the pci\_a begins the address phase by asserting framen and driving the address on the ad[31..0] bus and the command on the cben[3..0] bus.

In a DMA write (local side to PCI) transaction, the pci\_a first reads up to 16 DWORDS from the local side and stores them in its internal RAM buffer. At this point, the DMA asserts requ to acquire mastership of the PCI bus. After the arbiter asserts gntn, the pci\_a begins the address phase.

### Master Read Transactions

The pci\_a supports two types of master read transactions:

- Single-cycle master read

- Master burst read

### Single-Cycle Master Read Transaction

In a master read transaction, data is being transferred from the PCI side to the local side. Assuming the pci\_a has acquired mastership of the PCI bus, the start of a master read transaction is indicated when the pci\_a asserts framen.